- 您现在的位置:买卖IC网 > Sheet目录1990 > CDP68HC68T1M (Intersil)IC RTC 32X8 NVSRAM CMOS 20-SOIC

17

FN1547.8

October 29, 2007

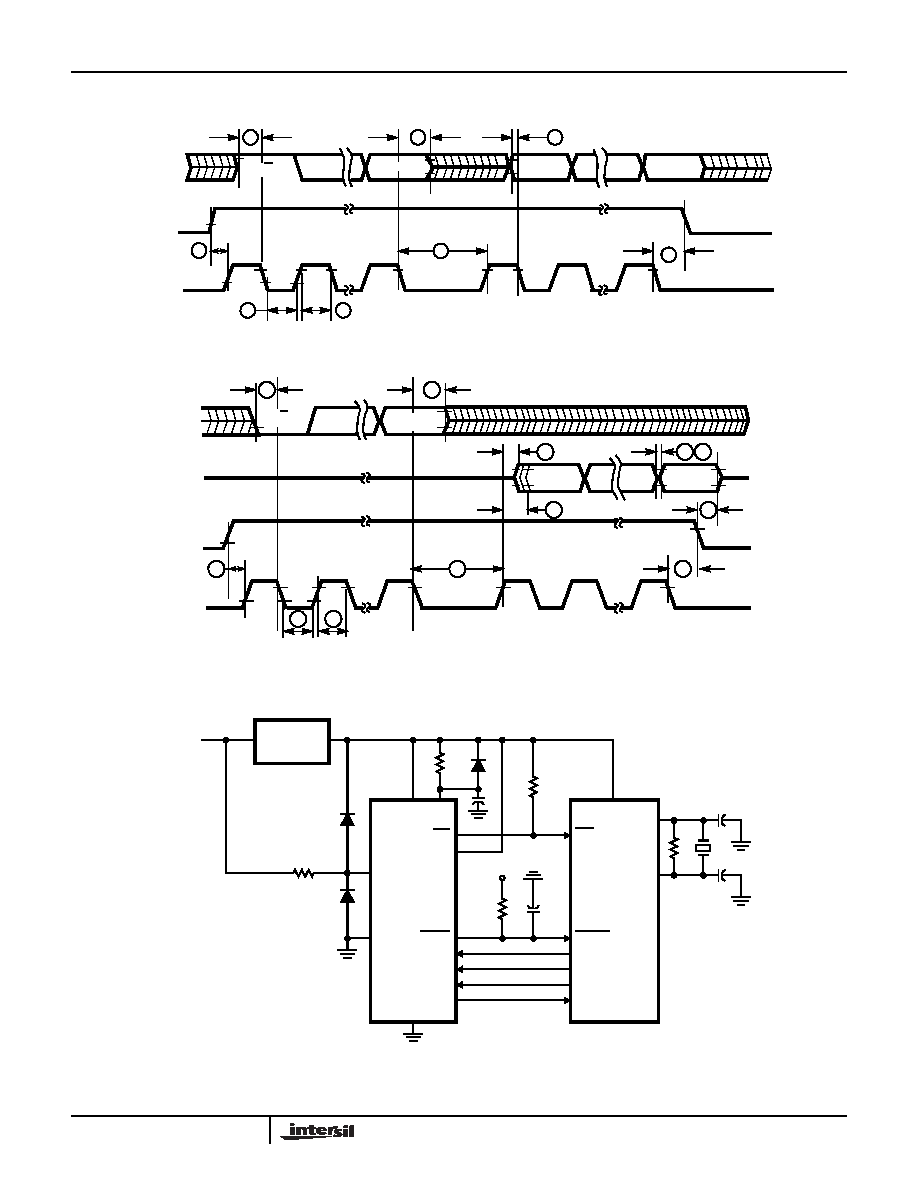

Timing Diagrams

FIGURE 14. WRITE-CYCLE TIMING WAVEFORMS

FIGURE 15. READ-CYCLE TIMING WAVEFORMS

5

A

5

I

2

3

4

C

MOSI

CE

SCK

W/R

A6

A0

D7O

D6O

D1N

DON

12

11

8

A

5

7

8

2

C

I

4

3

MOSI

MISO

CE

SCK

W/R

A6

A0

D7O

D6O

DIN

DON

System Diagrams

NOTE: Example of a system in which power is always on. Clock circuit driven by line input frequency.

FIGURE 16. POWER-ON ALWAYS SYSTEM DIAGRAM

VDD

IRQ

CDP68HC05C8B

RESET

PORT

SCK

MOSI

MISO

POR

VDD

INT

VSYS

LINE

CDP68HC68T1

CE

VBATT

CPUR

SCK

MOSI

MISO

XTAL IN

BRIDGE

REGULATOR

VDD

AC

LINE

CDP68HC68T1

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CPLL66-1600-2200

IC VCO PLL/SYNTH 2.2GHZ SMD

CPLL66-2175-2175

IC VCO PLL/SYNTH 2175MHZ SMD

CPLL66-2400-2500

IC VCO PLL/SYNTH 2500MHZ SMD

CPLL66-2450-2450

IC VCO PLL/SYNTH 2450MHZ SMD

CPLL66-3160-3380

IC VCO PLL/SYNTH 3380MHZ SMD

CPLL66-3475-3475

IC VCO PLL/SYNTH 3475MHZ SMD

CPLL66-4160-4380

IC VCO PLL/SYNTH 4380MHZ SMD

CPLL66-4240-4240

IC VCO PLL/SYNTH 4240MHZ SMD

相关代理商/技术参数

CDP68HC68T1M2

功能描述:实时时钟 PERIPH SPIAL-TIME- CLK 16W IND RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

CDP68HC68T1M296

功能描述:实时时钟 PERIPH SPIAL-TIME- CLK 16W INDEL RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

CDP68HC68T1M296S2357

制造商:Rochester Electronics LLC 功能描述:- Bulk

CDP68HC68T1M2Z

功能描述:实时时钟 PERI SPIAL-TIME-CLK RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

CDP68HC68T1M2Z96

功能描述:实时时钟 PERI SPIAL-TIME-CLK RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

CDP68HC68T1M96

功能描述:实时时钟 PERIPH SPIAL-TIME- CLK 20W INDEL RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

CDP68HC68T1M96S2357

制造商:Rochester Electronics LLC 功能描述:- Bulk

CDP68HC68T1MZ

功能描述:实时时钟 W/ANEAL PERIPH SPIAL -TIME-CLK 20W IND RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube